EUVIS公司坐落美國加州,規(guī)劃與出產(chǎn)全球頂尖的高速數(shù)模轉(zhuǎn)換DAC、直接數(shù)字頻率合成器DDS、復(fù)用DAC的芯片級產(chǎn)品,以及高速采集板卡、動態(tài)波形發(fā)生器產(chǎn)品。

其高速DAC芯片采樣率達(dá)到10Gsps,超高性價比,徹底滿意測驗、航空航天、雷達(dá)、軍事等運用要求。

直接數(shù)字頻率合成器DDS是Direct Digital Synthesizer的英文縮寫,是一項要害的數(shù)字化技術(shù)。與傳統(tǒng)的頻率合成器比較,直接數(shù)字頻率合成器DDS具有低成本、低功耗、高分辨率和快速轉(zhuǎn)換時刻等優(yōu)點,廣泛運用在電信與電子儀器范疇,是完結(jié)設(shè)備全數(shù)字化的一個要害技術(shù)。

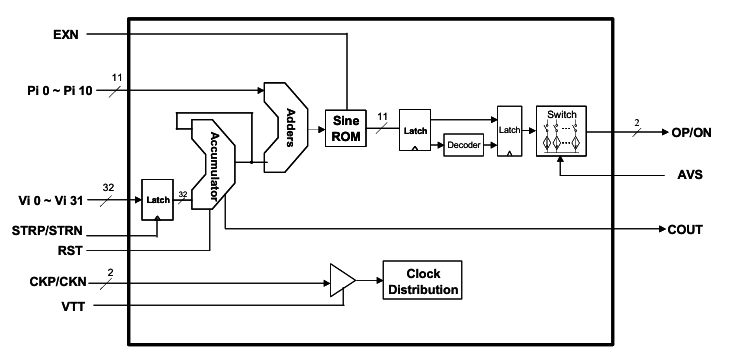

直接數(shù)字頻率合成器DDS主要由相位累加器、相位調(diào)制器、正弦ROM 查找表和D /A 構(gòu)成。相位累加器、相位調(diào)制器、正弦ROM查找表是DDS結(jié)構(gòu)中的數(shù)字部分, 由于具有數(shù)控頻率合成的功能,又合稱為NCO。

相位累加器是整個直接數(shù)字頻率合成器DDS系統(tǒng)的核心,在這里完結(jié)相位累加功能。頻率操控字還經(jīng)過一組寄存器, 該寄存器是同步的, 使妥當(dāng)頻率操控字改變時不會干擾相位累加器的作業(yè)。

相位調(diào)制器接納相位累加器的相位輸出, 在這里加上一個相位偏移值, 主要用于信號的相位調(diào)制,

如運用于通信方面的相移鍵控等, 不運用此部分時能夠去掉, 或者將其設(shè)為一個常數(shù)輸入。相同相位字

輸入也要用同步寄存器堅持同步。

正弦ROM查找表,完結(jié)fsin的查找表轉(zhuǎn)換,是相位到起伏的轉(zhuǎn)換, 內(nèi)部存有一個完好周期正弦波的

數(shù)字起伏信號,輸入是ROM 的地址值, 輸出送往D /A, 轉(zhuǎn)化成模擬信號。

在參閱時鐘fclk操控下,頻率操控字K與相位寄存器的輸出反饋在相位累加器中完結(jié)加運算,存入寄存器,作為下一次加運算的一個輸入值,相位累加器輸出高位數(shù)據(jù)作為波形存儲器的相位抽樣地址值,查找波形存儲器中相對應(yīng)單元的電壓幅值,得到波形二進(jìn)制編碼,完結(jié)相位到電壓幅值的改變。波形二進(jìn)制編碼再經(jīng)過D/A轉(zhuǎn)換器,把數(shù)字信號轉(zhuǎn)換成相應(yīng)的模擬信號。

累加器得到的相位是怎樣去尋址正弦ROM的,對于N位的相位累加器對應(yīng)2的N次方數(shù)量的相位累加值,假如正弦ROM中存儲的點數(shù)也是2的N次方的話,對存儲容量和資源的要求就比較高了,實際上在尋址正弦ROM表時,用的是相位累加值的高位,也就是說并不是每個時鐘fc都從正弦ROM表中取一個數(shù)值,而是多個時鐘取一個值,這樣能保證相位累加器溢出時,從正弦ROM表中取出正好一個正弦周期的樣點。因此,相位累加器每計數(shù)2的N次方次,對應(yīng)一個正弦周期。而相位累加器1秒鐘計數(shù)fc次,在k=1時,DDS輸出的時鐘頻率就是頻率分辨率。頻率操控字K增加時,相位累加器溢出的頻率增加,對應(yīng)DDS輸出的頻率變?yōu)?/span>K倍的DDS頻率分辨率。

設(shè)定:ROM存儲點數(shù)為1024,每個點是用8位二進(jìn)制表明。即,ROM地址線寬度為10,數(shù)據(jù)線寬度為8。

相位調(diào)制器位寬M=10,那么依據(jù)DDS原理,相位累加器位寬N=20。那么在相位調(diào)制器中與相位操控字進(jìn)行累加時,運用相位累加器的高10位累加。

而相位累加器的低十位只與頻率操控字累加。為什么是這姿態(tài)?

咱們以頻率操控字K=1為例,相位累加器的低十位一直會加1,直到低十位溢出向高十位進(jìn)位,此時ROM地址應(yīng)該是0,也就是說,ROM的0地址中的數(shù)據(jù)被讀了1024次,繼續(xù)下去,ROM中的1024個點,每個點都將會被讀1024次,終究輸出的波形頻率應(yīng)該是參閱時鐘頻率的1/1024。反過來想,周期被擴大了1024 。相同當(dāng)頻率操控字為10時,相位累加器的低十位一直會加10,那么,相位累加器的低十位溢出的時刻比上面會快十倍,則ROM中的每個點比較于上面會少讀10次,所以終究輸出頻率是上述的10倍。這就是直接數(shù)字頻率合成器DDS。

直接數(shù)字頻率合成器DDS終究輸出的正弦波的幅值,有必要都是ROM表中的正弦幅值。頻率操控字K的最大值應(yīng)小于2的N次冪除以2,累加器數(shù)據(jù)位寬20位,ROM表地址位寬10位,在終究ROM表尋址時,用的是累加器的高10位,而低10位只用來進(jìn)行累加。由于咱們上述說DDS終究輸出正弦波的賦值有必要是ROM表中的幅值,也就是說,ROM表中的幅值有必要都被用到,而不能越過。以累加器位寬20位為例,它的一半是1024,當(dāng)頻率操控字以超越1024累加時,高十位輸出累加值會超越1,也就是在尋址ROM表時越過某些賦值。依據(jù)上述能夠得出結(jié)論了,頻率操控字K的最大值應(yīng)小于2的N次冪除以2。

深圳市立維創(chuàng)展科技是EUVIS數(shù)模轉(zhuǎn)換器的代理經(jīng)銷商,主要提供EUVIS的DAC、DDS、DAC等產(chǎn)品,原裝現(xiàn)貨,價格優(yōu)勢,歡迎咨詢